Computer on a Chip

The Silicon Platform for the Internet of Things

The Silicon Platform for the Internet of Things

The Internet of Things (IoT) broadly describes the entire emerging segment of connected and pervasive computing systems and platforms. These systems will have wide-ranging silicon technology requirements depending on the end application.

As discussed in prior posts (here and here), IoT represents the next wave of computing and will be enabled by reimagined silicon and software platforms.

Datacenters will form the back end of the IoT and serve as the repository of all the data generated by a vast array of connected applications, including consumer, industrial, medical, and environmental, which will form the front end. The front-end devices will in turn have a wide range of performance and power requirements.

While the PC was enabled by the CPU platform and the smartphone was enabled by an integrated SoC platform, the front-end devices of the IoT are likely to be enabled by a new, even more integrated silicon platform —System-in-Package (SiP). By virtue of its functionality, this platform can be considered a Computer-on-a-Chip.

This new platform will have three basic components —

(1) A compute element (e.g. CPU or MCU)

(2) A connectivity element (e.g. radio)

(3) A multitude of sensors (e.g. temperature, motion, biometric, etc)

An excellent example of this platform is the S1 package at the heart of the Apple Watch (see picture below). This little package is composed of over 30 individual chips/sub-systems all assembled into a single sealed package. It is also important to note that the vast majority of this silicon is not at the cutting edge of Moore’s Law. In fact, most of the silicon is made on legacy technologies that are several generations old. The chips come from multiple foundries, multiple design houses and also include MEMS components in addition to CMOS and memory. Arguably, the most striking technological achievement in the S1 is not the application processor itself or any single chip. The most remarkable achievement is the packaging technology that enabled so many discrete components to be tightly integrated into a single standalone module. The individual components appear to be generic, ultra-low cost, off-the-shelf chips — Apple’s innovation and competitive advantage is in the integration of the package itself.

The vast majority of silicon shipped in the future is likely to be along the lines of the S1 package (modular and fully integrated compute, connectivity and sensor elements). The composition and specifications of these components will vary based on end application. However, the price point for such a package in the future is likely to be $10 or even less. The total BOM for the silicon in the S1 package is estimated to be under $30!

This new platform will reshape the contours of the entire semiconductor industry in the years to come, just as the SoC reshaped the industry by enabling mobile computing.

A Spectrum of Performance/Power/Cost

Wearable technologies such as Microsoft HoloLens and Facebook Oculus represent a class of devices that rely on massive computing, imaging and video and will need high performance (multicore, GHz frequency) and low power. On the other hand, fitness trackers such as Fitbit and Jawbone’s UP represent a category of devices that employ location sensing, motion sensing, and modest (less than 100 MHz) computing. Apple Watch falls somewhere in between these extremes where high performance and low power are equally paramount. A little temperature sensor that records data in a remote oil field and sends it to the cloud may not need much compute power at all, but it will need extremely low standby power and very long battery life in addition to extreme temperature stability.

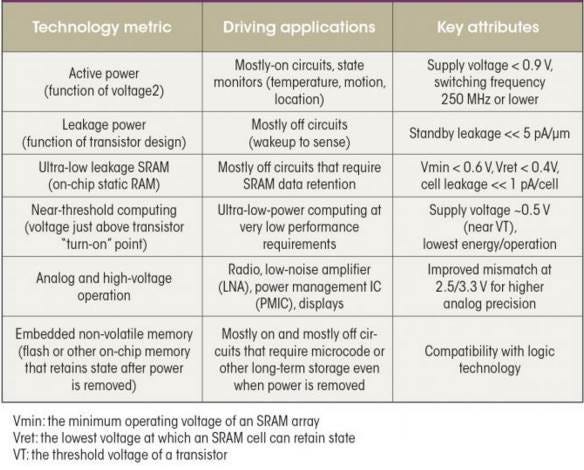

Regardless of the end application, the focus of transistor development over time will shift from “performance-per-watt” to “energy-per-operation.” Many of the sensing platforms and devices that will become part of the IoT will need to have battery life on the order of months or years (e.g., remote infrastructure monitoring). Many more will require battery life on the order of weeks or months (e.g., wearable technologies). And yet many more will harvest or scavenge energy and run on no battery at all (e.g., medical patches). Many of these applications are likely to be single use and replaced upon battery discharge. Since many of them must be off or in a standby state while retaining a sizable amount of data, ultra-low standby power is crucial in addition to low active power. An ideal IoT platform will be able to meet these attributes and provide designers the flexibility to incorporate any combination of them on a single chip (see table below).

Making it Smaller Doesn’t Help Anymore

A transistor platform that supports these specifications at the lowest system cost will win in the IoT/wearables space.

Unlike CPU technology, the transistors that make up this platform are not limited by geometrical (pitch) scaling. For example, analog and high-voltage (1.8V/2.5V/3.3 V) blocks have not been scaled over several logic technology generations due to very stringent requirements on variability matching. The most advanced embedded non-volatile memory (e-NVM) technology in production today uses design rules that are four times larger than the most advanced logic technology. As a result, chips that are dominated by analog/e-NVM do not benefit from the geometrical scaling of logic transistor densities.

Based on these requirements, 40/55/65nm technologies are best suited to support the bulk of the front-end IoT and more specifically the wearable technologies space in the near term (2–3 years). The Newton platform by Ingenic Semiconductor is one such integrated computer-on-a-chip (Link).

The Apple Watch, arguably the most sophisticated “wearable” technology today uses a 28nm SoC as the backbone of its S1 multi-chip module. It is instructive to note that in spite of being a category defining product, the initial Apple Watch used n-2 (28nm) technology and not the latest 20nm/16nm technologies. Over time, products like Apple Watch which can command a high premium will migrate to advanced silicon technology, however, even three to five years out, a large swath of the high-end IoT space likely will continue to be served by 28nm planar transistor technology while the bulk of the IoT space will utilize 40nm technology, provided a suitable e-NVM solution can be developed by then.

Given the requirements of cost, power, and functional integration, it is unlikely that sub-20-nm transistor technology will serve the mainstream IoT or wearable technologies space for another five to seven years, if ever. Once a starting technology is in place for such applications, an enhancement roadmap will be driven not so much by geometric scaling, but more by aggressively lowering the power envelope and integration of more functionality within an existing footprint. A leading indicator of this trend is the unprecedented range and variety of TSMC’s 28nm technology offering (28HPM, 28HPC, 28ULP, 28HP, 28LP to name a few), which is an attempt by the foundry to cater to widely varying cost/performance/power requirements at a single geometry. This trend also enables a slower cadence for Moore’s Law by allowing massive re-use of the same technology over longer periods of time. At the same time, the foundry roadmaps are beginning to reflect a stronger emphasis on semiconductor packaging technologies (e.g. 2.5D packages, 3D packages, Thru-Silicon-Vias, etc). While conventional Moore’s Law scaling is slowing down, these “More than Moore” technology roadmaps are likely to accelerate even faster.

The next post will discuss the impact of IoT computing on the battle for architecture dominance (x86 v ARM) and the larger impact of the chip wars on the semiconductor foundry landscape.